FPGA

Vitis开发过程中遇到的错误

没找到具体原因。 先生成 boot. Bin 文件烧录到内存卡后再启动 zynq 就不会出现这个报错。

解决方案

将开发板的 boot 选项从 SD 切换到 jtag 即可

在 Linux 环境下和 win 环境下创建工程添加 stdio 库时都会有这个问题。

解决方案

Pr…

Xilinx FPGA中的BUFFER

FPGA 大型设计中推荐使用同步时序电路,同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动有更高的要求。为满足时序的要求,一般采用全局时钟资源驱动设计的主时钟,FPGA 的主时钟一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构。 1.1 缓冲

输入输出缓冲…

黑金Alinx xc7z020 原理图

1.1 CLK:U18 2.1 RST:N15

3.1 J10

3.2 J11

8bit数据转1bit逐位输出电路仿真

在 DVB-S 系统中,TS 流在经过 RS 编码后,会变成 uint8 类型的数据,在后续 QPSK 星座映射时又需要二进制码流,因此在进行了 RS 编码后要将 8 个 bit 的数据转化成 1 个 bit 逐位输出 首先使用 BitwiseOperator 模块按位与操作…

MATLAB中使用HDL Coder生成HDL代码时的报错集合

1.1 产生原因 由于时序考虑,在每个模块的输出端添加了 1 到 2 级的输入输出流水线,但是在这种带反馈的结构上添加输入输出流水线后,会产生如下的报错

可以看出加入的输入输出流水线会导致额外的时钟延时,使得延时平衡失败。

1.2 解决方法

在保证时序的前提下将带有反馈回路…

Modelsim中使用tcl命令导出仿真数据到txt文件

参考下面的 CSDN 博客 bookmark

Copy

proc write_sim_data {env name radix cycle file} {

set fid [open $file w]

for {set i 0} {$i <= $::now…

Matlab生成txt文件导入到Vivado仿真

Copy %% Txt Generate

pre_RS_data=dec2bin(simDataIn,8); %将数据转化为8bit的二进制

fid=fopen("F:\FPGA\Xilinx_vivado\project\dvbstestbench\dbvs…

Vivado报错集合

这个错误通常表示在使用 vvdo 进行逻辑分析时出现了问题。错误信息表明,存在一个断言失败,即在获取探针数据时,数据不匹配。 报错代码

Copy

[Synth 8-5535] port <clk_0> has illegal connections. It is illegal…

有限字长效应

数字信号处理的实质为数值运算。运算过程中,系统中的系数、输入输出等都要以二进制的形式存储在有限长的存储单元中,此时有限长度的数的精度就是有限的。具体实现中可能会产生误差。在数字系统中因有限字长引起误差的因素主要为以下三种: AD…

AXI DMA+AXI-S FIFO回环学习

DMA 是现代计算机的特色之一,是硬件实现存储器与存储器、存储器与 I/O 设备之间直接进行高速数据传输的内存技术,它允许不同速率的设备进行沟通,而不需要依靠 CPU 的中断负载。 如果不使用 DMA,那么 CPU 需要从数据源把每一个片段的数据复制到寄存器中…

Vivado中关于综合的设置

0.1.1 1. 综合策略(Synthesis Strategy) 作用:控制综合工具优化设计的方向(性能、面积、功耗)。

选项:

Vivado Synthesis Defaults:默认策略,平衡性能和资源。

AreaOptimized_high:优先减少资源占用(如…

Petalinux报错记录

编译时卡住,检查 build.log 发现 log 文件提示 Unable to connect to bitbake server,此时只需要将 build 文件夹下的 bitbake.lock 删除即可 在最新版的 UG1144 (v2022.2) 文档中…

Petalinux

参考《UG 1157 PetaLinux Command Line Reference Guide》

Copy

//创建petalinux工程

petalinux-create -t project --template zynq -n <name>

//配置工程

cd…

多频点数字上变频器-调试记录

通过 mm-s-fifo 将 PS 侧的 GP 接口转化为 stream 接口。

2025-3-14

可以看出 mm-s-fifo 的输出一直没变,后级的 ready 信号可能有问题。

mm-s-fifo 的 valid 信号有问题

解决方法

勾选 cut…

FIFO

FIFO 本质是由 RAM 加上读写逻辑构成的先入先出的数据缓冲器。与 RAM 的区别是 FIFO 没有外部读写地址线,顺序写入顺序读出数据,其数据地址是由内部读写指针自增完成,因此 FIFO 在读写时不需要考虑读写冲突的问题。 根据 FIFO 工作的时钟域,可以分为同步…

FPGA开发时序图绘制

开始的时候画时序图都是拿 visio 硬连,但是那个线宽太难统一了,丑不拉几的,遂学习 waveform 语法使用代码来画时序图。 开始

Vscode 中安装 waveform render 或者在 GitHub 搜索 wavedrom 安装即可。由于 vscode…

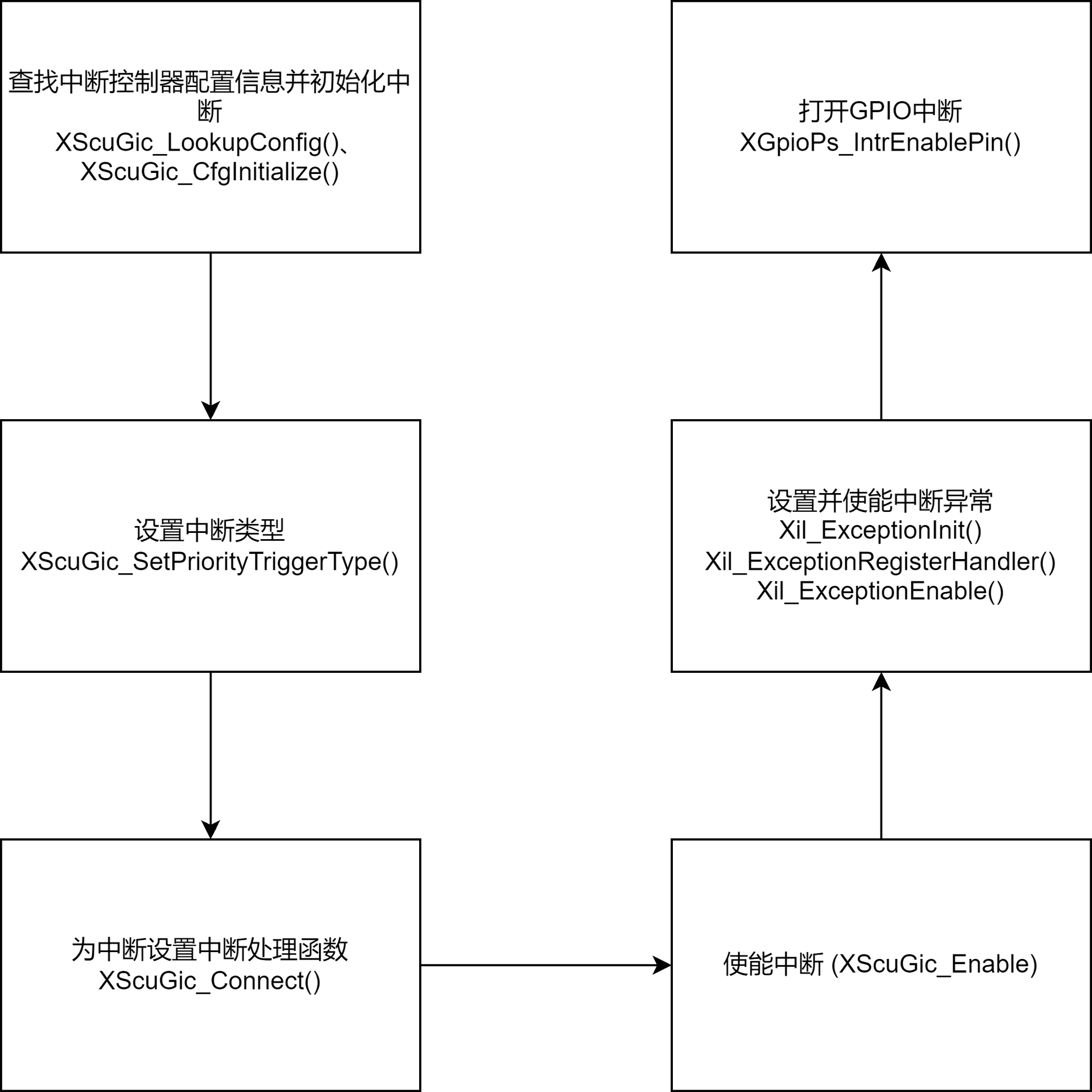

ZYNQ-PS GPIO中断过程

查找中断控制器配置信息并初始化中断控制器驱动(XScuGic_LookupConfig、XScuGic_CfgInitialize) 设置中断类型(XScuGic_SetPriorityTriggerType)

为中断设置中断处理函数(XScuGic_Connect)

使能中…

ZYNQ-IP-AXI-GPIO

AXI GPIO 可以将 PS 端的一个 AXI 4-Lite 接口转化为 GPIO 接口,并且可以被配置为单端口或双端口,每个通道的位宽可以独立配置。 通过使能三态门可以将端口动态地配置为输入或输出。

AXIGPIO 是 ZYNQ PL 端的一个 IP 核,可以将 AXI…