1 基本原理#

級聯積分コームフィルター(Cascade Integrator Comb)は、多速率信号処理において非常に効率的なデジタルフィルターです。CIC フィルターはローパスフィルターの特性を持ちながら、以下の利点があります:

- フィルター係数がすべて 1 であり、設計時にフィルター係数を保存する必要がなく、ストレージユニットを節約し、フィルタリング時には加算器と累積器のみが必要で、乗算器は不要です。

- 構造が規則的であり、全体の構造に影響を与えずに補間因子を柔軟に設定できます。

1.1 積分器#

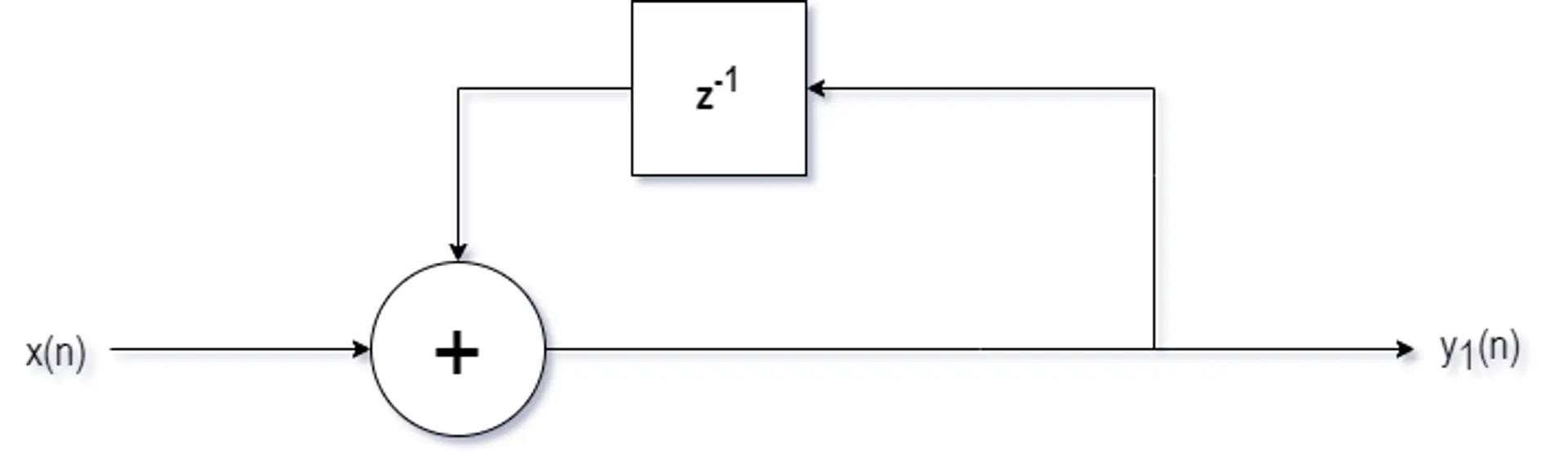

積分器の構造は

時域では次のように表されます

y1(n)=x(n)+y1(n−1)

周波数域では次のように表されます

H1(ejw)=1−e−jw1

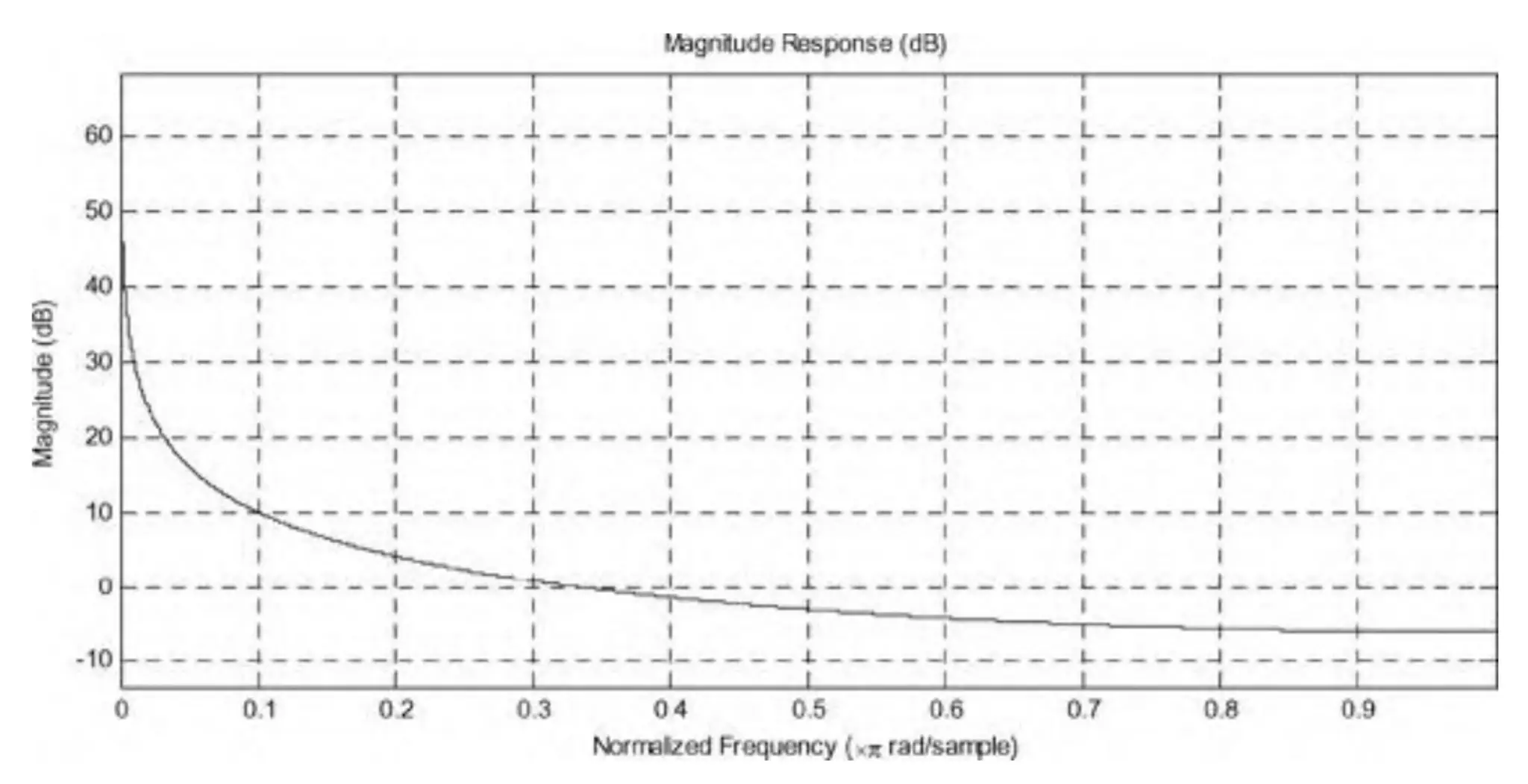

積分器の振幅スペクトルは次のようになります

H1(ejw)=1−e−jw1=e−jw/2(ejw/2−e−jw/2)1=2sin(2w)1

この式から、積分器は極点 $(\omega = 2k \pi,k は整数)$ のみを持ち、零点は持たず、直流信号に対して無限大の増幅を持つことがわかります。

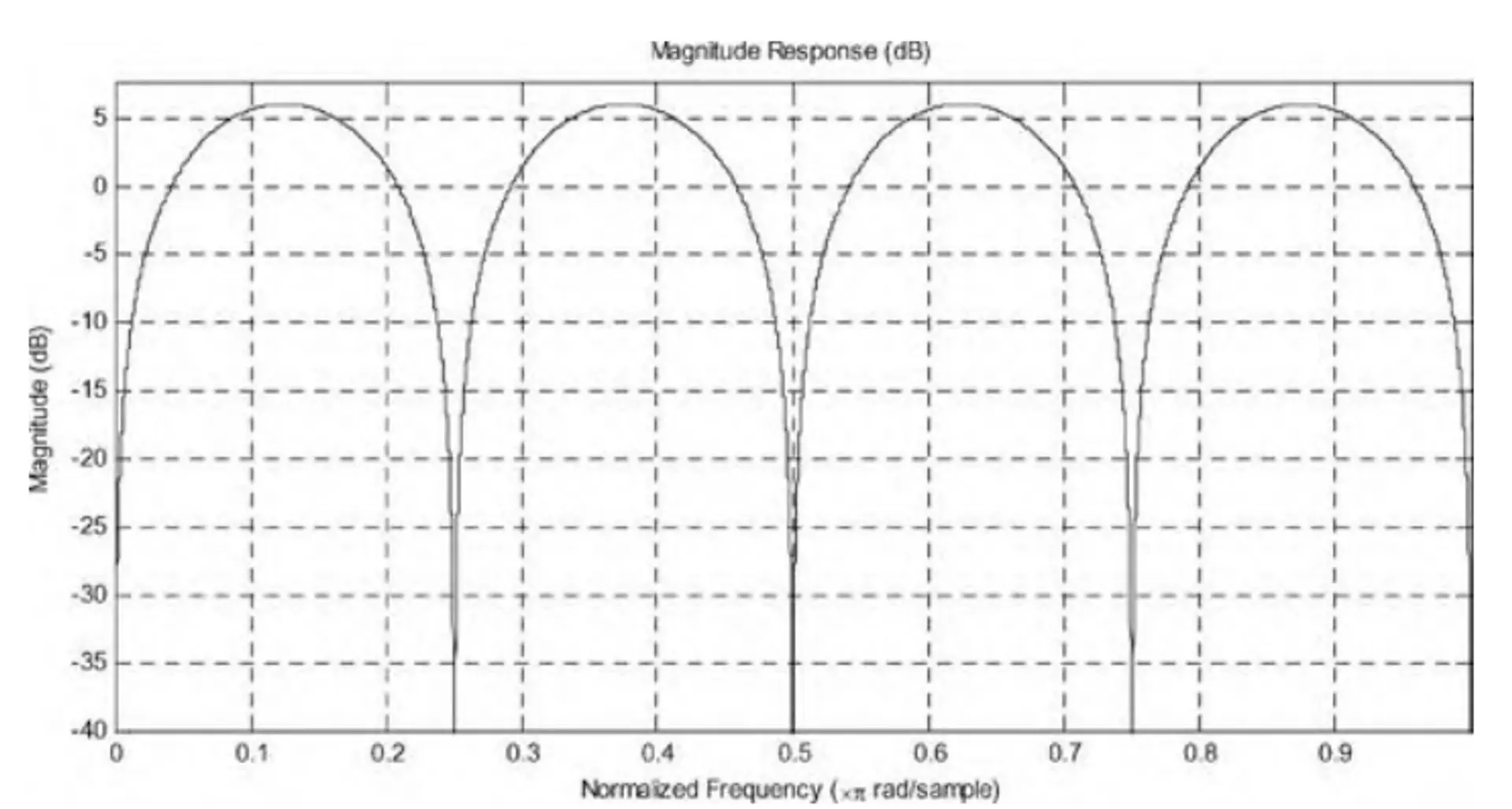

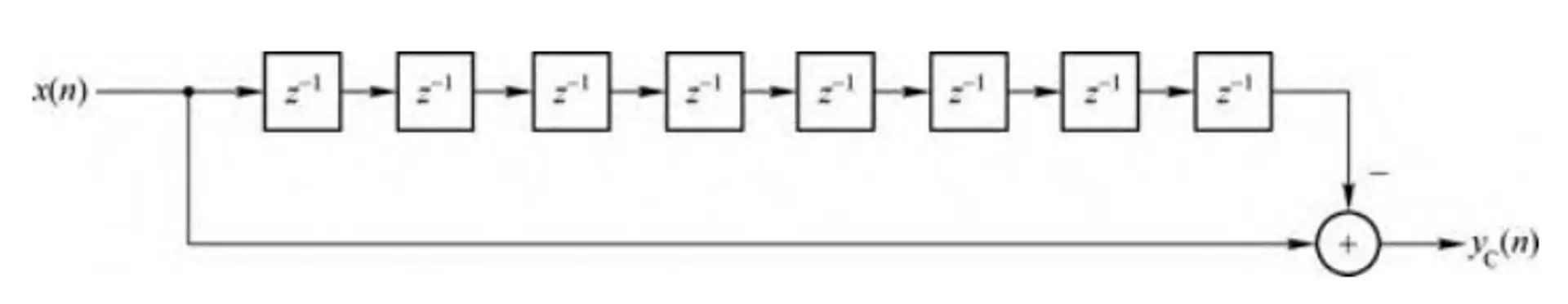

1.2 コームフィルター#

時域では次のように表されます

yC(n)=x(n)−x(n−RM)

ここで

周波数域では次のように表されます

HC(z)=1−z−RM

振幅スペクトルは次のようになります

HC(ejw)=1−e−jRMw=e−jRMw/2(ejRMw/2−e−jRMw/2)=2sin(2RMw)

コームフィルターは零点のみを持ち、極点は持たないことがわかります。

R=8、M=1 の場合、構造は

これにより、単一級 CIC フィルターの振幅スペクトルは次のようになります

HCIC(ejw)=H1(ejw)⋅HC(ejw)=sin(2w)sin(2RMw)

$\mathrm {RM\omega}/2=\mathrm {k}:\pi $ のとき、すなわち $w=\frac {2k\pi}{RM}\quad (k=\pm1,\pm2,\cdots,\pm (RM-1))$ のときに零点が決定されます。

$\omega /2 =k\pi$、すなわち $\omega = 2k\pi$ のとき、このときの振幅周波数応答は次のようになります

HCIC(ejω)ω=2kπ=RM

これにより、零点と極点が相殺されます。

単一級 CIC フィルターは $\omega =0$ のとき $\left| H_{CIC}(e^{j\omega}) \right|=RM$ であり、したがって主瓣の範囲は $\begin {bmatrix} 0,\frac {2\pi}{RM}\end {bmatrix}$ であり、残りはすべて副瓣であり、第一副瓣レベルは

A1=HCIC(ejw)w=RM3π=sin(21×RM3π)sin(2RM×RM3π)=sin(2RM3π)1

したがって、副瓣抑制は

A=RMsin(2RM3π)

$\mathrm {R}\rightarrow\infty $ のとき、副瓣抑制は

A=20lg(R→∞limA)=20lg(23π)=13.46dB

単一級 CIC フィルターの阻止帯減衰は

α=−20lgb

通帯リップル(通帯波形の変動)は

δ=20lgsin(bπ)bπ

ここで b は帯域幅比率因子です。

b=fs/(RM)B

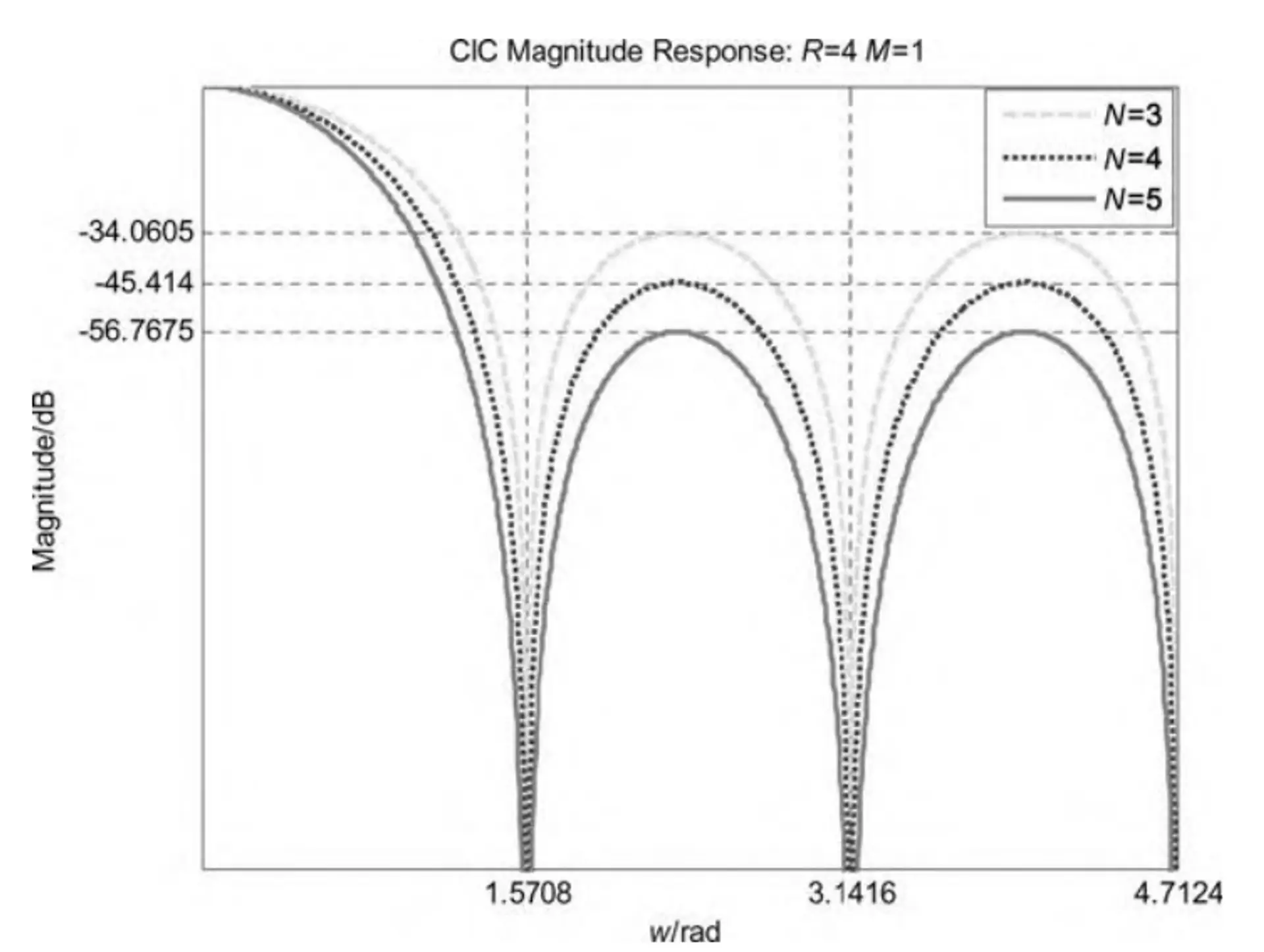

単一級 CIC フィルターの副瓣レベルは高いため、多段 CIC 級聯によって改善できます。

H(ejw)=sin(2w)sin(2RMw)N

N 段 CIC 級聯フィルターに対して、副瓣抑制、阻止帯減衰、通帯リップルは次のように表されます

⎩⎨⎧AN=13.46NdBαN=−20NlgbδN=20Nlgsin(bπ)bπ

CIC フィルターの次数を増やすと、副瓣抑制と阻止帯減衰を増加させることができますが、通帯リップルが大きくなります。したがって、通帯性能を考慮して、通常は $N\leq5$ を選択します。N が不変のとき、帯域幅比率因子 b が小さいほど、CIC フィルターの通帯と阻止帯特性も良くなるため、CIC は通常、補間システムの最後の段に配置されます(入力レートが最も高い)。

2 ビット成長問題#

多段フィルターの振幅周波数応答から、$\omega \rightarrow 0$ のとき

w→0limH(ejw)=w→0lim21⋅cos(w/2)2RM⋅cos(RMw/2)N=(RM)N

これにより、多段 CIC フィルターが引き起こす可能性のある最大の振幅増益は

Gmax=(RM)N

入力データ $x (n)$ が符号付き数で、ビット幅が $B_{in}$、値の範囲が $[-2^{B_{in}-1},2^{B_{in}-1}-1]$ であると仮定すると、出力 $y (n)$ の最大値は

ymax=−2Bm−1⋅(RM)N

したがって、出力の最大ビット幅は

Bout=ceil[log2∣ymax∣]+1=N⋅ceil[log2(RM)]+Bin

FPGA 設計では、出力信号のビット幅を適切に設定し、データのオーバーフローを防ぐ必要があります。リソースを節約するために、各段で適切にビットを切り捨てることもできます。

3 Matlab での CIC 補償フィルター設計#

CIC フィルターは通帯内が平坦でないため、前段に CIC 補償フィルターを追加する必要があります。Matlab の対応する関数はfdesign.ciccompで、構文は次のとおりです。

d = fdesign.ciccomp

d = fdesign.ciccomp(d,nsections,rcic)

d = fdesign.ciccomp(...,spec)

h = fdesign.ciccomp(...,spec,specvalue1,specvalue2,...)

ここで、コームフィルターの遅延長は d、フィルターの次数は nsections、CIC レート変換因子は rcic です。

3.1 例#

h = fdesign.ciccomp;

set(h,NumberOfSections=5,DifferentialDelay=1);

cicComp = design(h,'equiripple',SystemObject=true);

filterAnalyzer(cicComp)